| Aluno Nº |  |

|----------|--|

|----------|--|

# Instituto Superior Técnico Licenciatura em Engenharia Aeroespacial Licenciatura em Engenharia Electrotécnica e de Computadores

#### Sistemas Digitais

Exame de 2ª Época – 17 de Julho de 2003

## Antes de começar o exame leia atentamente esta folha de rosto

- 1. A mesa de exame apenas deve ter a identificação do aluno (<u>cartão de estudante</u> e <u>bilhete de</u> identidade ou outro documento oficial com fotografia)

- 2. <u>Identifique todas as folhas do enunciado</u>. A não identificação de uma folha de exame acarreta a sua <u>destruição automática</u>.

- 3. Responda apenas na folha de exame. Utilize as costas das folhas para rascunho.

- 4. Para cada questão do exame é fornecido um espaço, devidamente enquadrado, dentro do qual deverá responder. O tamanho do enquadramento está ajustado ao tamanho expectável da resposta. Respostas que se prolongam para além do enquadramento de cada pergunta apenas significam que o aluno está a responder desadequadamente, pelo que serão devidamente penalizadas.

- 5. As cotações das perguntas encontram-se indicadas à esquerda, a cheio entre parêntesis.

- 6. Todas as respostas têm de ser justificadas adequadamente.

- 7. Duração do exame: 2 horas e meia.

- 8. A não entrega do exame tem o mesmo significado que a não comparência ao exame.

| Aluno Nº |

|----------|

|----------|

#### Grupo I – Circuitos Combinatórios Básicos

- 1. Considere a função  $f(A,B,C,D,E) = \sum m(0,2,3,4,5,8,13,14,16,21,24,26,27,29,31) + \sum m_d(6,10,12,18,20,28)$ .

- a) [0,5 val] Complete o mapa de Karnaugh,

|    |    | A=0 |    |    |

|----|----|-----|----|----|

|    | DE |     |    |    |

| BC | 00 | 01  | 11 | 10 |

| 00 |    |     |    |    |

| 01 |    |     |    |    |

| 11 |    |     |    |    |

| 10 |    |     |    |    |

|    |          | A=1 |    |    |

|----|----------|-----|----|----|

| ВС | DE<br>00 | 01  | 11 | 10 |

| 00 |          |     |    |    |

| 01 |          |     |    |    |

| 11 |          |     |    |    |

| 10 |          |     |    |    |

b) [1 val] Indique um Implicante primo essencial e um Implicante primo não Essencial. Justifique.

c) [1,5 val] Utilize o método Karnaugh para obter a expressão mínima da função f (A,B,C,D,E) como uma soma de produtos.

| Αlι      | uno                                                                                             | Nº        |

|----------|-------------------------------------------------------------------------------------------------|-----------|

| 2.       | [1 val] Determine a veracidade ou falsidade da relação                                          |           |

|          | $(A+B)\cdot (\overline{A}+C)\cdot (B+C) \Leftrightarrow (A+B)\cdot (\overline{A}+C)$            |           |

|          |                                                                                                 |           |

|          |                                                                                                 |           |

|          |                                                                                                 |           |

|          |                                                                                                 |           |

|          |                                                                                                 |           |

| 3.       | Considere a função lógica                                                                       |           |

|          | $f(A, B, C, D) = (A+B) \cdot C + (\overline{B}+D) \cdot (A+C)$                                  |           |

|          | a) [1 val] Efectue a manipulação da função f(.) de modo a ser realizada com portas lógicas NOR  |           |

|          |                                                                                                 |           |

|          |                                                                                                 |           |

|          |                                                                                                 |           |

|          |                                                                                                 |           |

|          |                                                                                                 |           |

|          |                                                                                                 |           |

| <u> </u> | b) [0,5 val] Desenhe o logigrama correspondente à implementação da função f(.) com portas lógic | icas NOR. |

|          |                                                                                                 |           |

|          |                                                                                                 |           |

|          |                                                                                                 |           |

|          |                                                                                                 |           |

|          |                                                                                                 |           |

|          |                                                                                                 |           |

|          |                                                                                                 |           |

|          |                                                                                                 |           |

| Aluno | Nº |

|-------|----|

|       | 1  |

#### Grupo II - Circuitos Combinatórios Integrados, Memórias

- 1. Pretende-se projectar um circuito que recebe um número binário de 3 bits  $(a_2a_1a_0)$  e indica na respectiva saída  $(b_1b_0)$  o número de 1s existentes em  $(a_2a_1a_0)$ . Exemplo para  $a_2a_1a_0=101$ obtém-se  $b_1b_0=10$  (2 em binário)

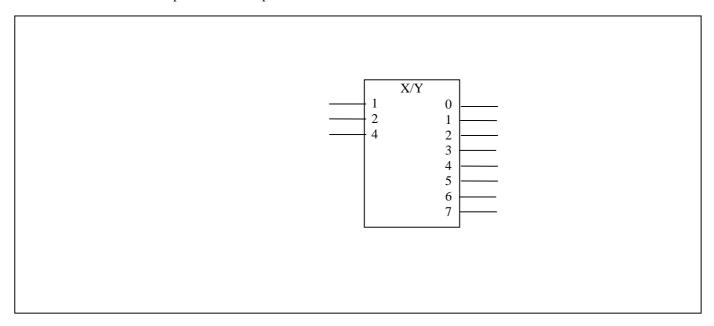

- a) [1 val] Implemente o circuito utilizando o descodificador indicado na figura. Atenção: Só pode utilizar portas adicionais do tipo OR e/ou do tipo AND.

b) [1,5 val] Determine o tempo de propagação máximo do circuito realizado em a).

Utilize os dados seguintes e justifique a sua resposta.

|     |          |    | TpLH  | TpHL  |

|-----|----------|----|-------|-------|

| X/Y | Níveis   | de | 20 ns | 39 ns |

|     | atraso 2 |    |       |       |

|     | Níveis   | de | 25 ns | 37 ns |

|     | atraso 3 |    |       |       |

| OR  |          |    | 18 ns | 20 ns |

| AND |          |    | 22 ns | 15 ns |

| Aluno Nº |  |

|----------|--|

|----------|--|

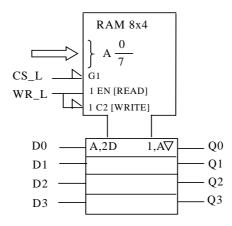

2. Pretende-se utilizar circuitos de memória, cujo símbolo é indicado a seguir, para realizar uma memória com 16 palavras de 8 bits cada.

a) [0,5 val] Indique o número de circuitos RAM 8x4 necessários. Indique também o número de bits que são necessários para endereçar as 16 palavras. **Justifique**.

b) [1 val] Esboce o esquema de ligações dos circuitos RAM 8x4 de modo a construir o circuito que é pedido.

| Nº |

|----|

|----|

#### Grupo III - Contadores e Registos

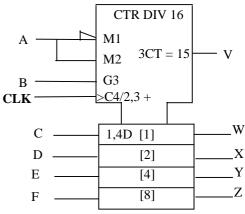

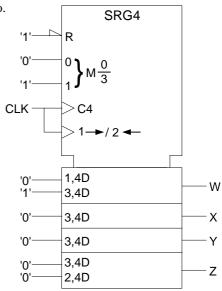

- 1. Considere o contador que se encontra na figura, no lado direito.

- a) [1 val] Admita que o contador está inicialmente no estado 10. Determine os valores lógicos nas entradas do contador para que, após 1 impulso positivo de relógio, o contador passe a ter nas saídas os valores indicados abaixo.

|                  | Z | Y | X | W | V |

|------------------|---|---|---|---|---|

| Inicialmente     | 1 | 0 | 1 | 0 | 0 |

| Após Impulso CLK | 1 | 1 | 1 | 1 | 0 |

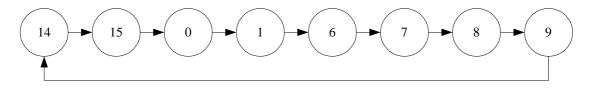

b) [2 val] Utilizando o contador e uma única porta lógica discreta adicional realize um circuito que efectue a sequência de contagem seguinte. Justifique.

| Aluno | Nº |

|-------|----|

| Aluno | N° |

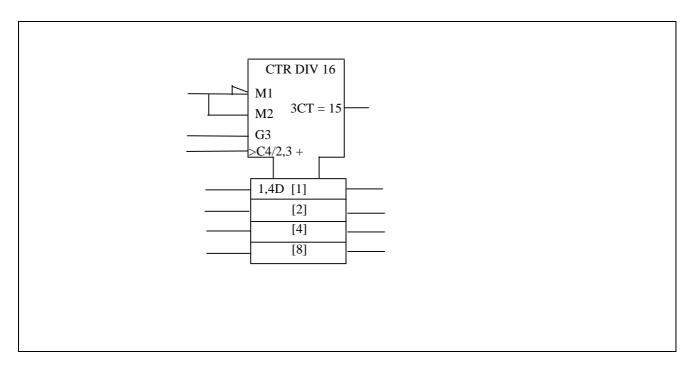

- Considere o registo de deslocamento que se encontra na figura, no lado direito.

- [1 val] Admita que o registo está inicialmente no estado (W, X, Y, Z) = (1, 1, 1, 0).Mantendo constantes os valores lógicos indicados nas entradas,

indique quantos ciclos de relógio são necessários para que

W, X, Y e Z assumam os valores (1, 0, 0, 0)? Justifique.

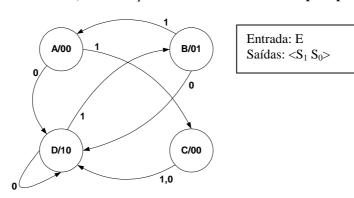

Grupo IV - Circuitos Sequenciais Síncronos

1. Considere a máquina de estados, com uma entrada E e 2 saídas S<sub>1</sub> e S<sub>0</sub>, definida pelo diagrama de estados seguinte. Projecte (de acordo com as alíneas abaixo) circuitos que a concretizem utilizando Flip-Flops D "edge-triggered" positivos.

[2 val] Determine as equações de excitação dos FFs e as funções das saídas, para uma concretização do circuito utilizando 1FF/estado ("one-hot enconding").

| Aluno | Nº |

|-------|----|

|-------|----|

b) [2 val] Determine as equações de excitação dos FFs e as funções das saídas, para uma concretização do circuito utilizando síntese clássica (usando o menor nº possível de FFs) e com a codificação de estados abaixo indicada:

|   | Q1 | Q0 |

|---|----|----|

| A | 0  | 0  |

| В | 0  | 1  |

| С | 1  | 0  |

| D | 1  | 1  |

|   |    |    |

|   |    |    |

| Aluno                                                                     | Nº |   |

|---------------------------------------------------------------------------|----|---|

| c) [1 val] Desenhe o logigrama correspondente ao circuito definido em b). |    | _ |

|                                                                           |    |   |

|                                                                           |    |   |

|                                                                           |    |   |

|                                                                           |    |   |

|                                                                           |    |   |

|                                                                           |    |   |

|                                                                           |    |   |

|                                                                           |    |   |

|                                                                           |    |   |

|                                                                           |    |   |

|                                                                           |    |   |

|                                                                           |    |   |

|                                                                           |    |   |

|                                                                           |    |   |

|                                                                           |    |   |

|                                                                           |    |   |

|                                                                           |    |   |

|                                                                           |    |   |

|                                                                           |    |   |

| Nº |

|----|

|----|

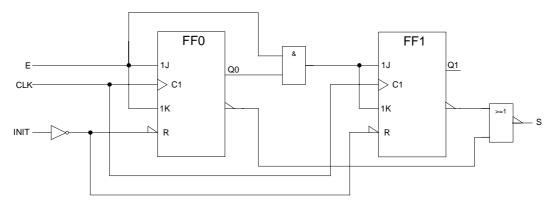

### 2. Considere o circuito sequencial abaixo.

| Parâmetros | FF                |      | AND  | NOR  | NOT |

|------------|-------------------|------|------|------|-----|

| tSU        |                   | 3ns  |      |      |     |

| tH         |                   | 1ns  |      |      |     |

| tPHL       | de CLK para Q, Q' | 15ns | 10ns | 20ns | 5ns |

| tPLH       | de CLK para Q, Q' | 10ns | 15ns | 15ns | 5ns |

| tPHL       | de R,S para Q, Q' | 5ns  |      |      |     |

| tPLH       | de S,R para Q, Q' | 5ns  |      |      |     |

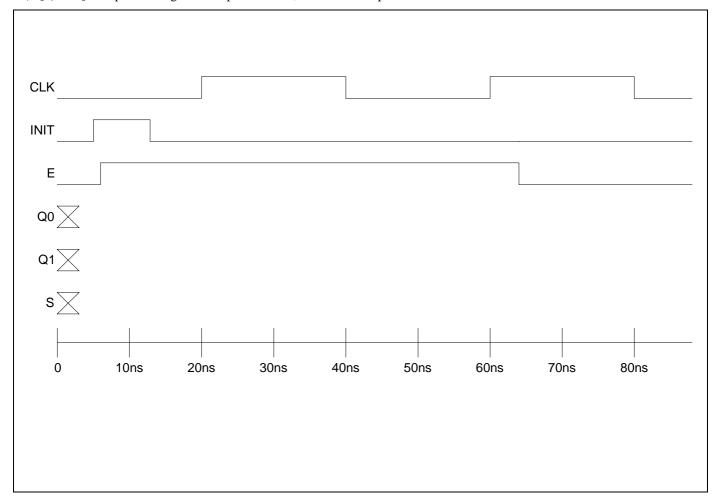

a) [1,5 val] Complete o diagrama temporal abaixo, considerando que o estado inicial do circuito é desconhecido.