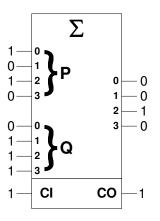

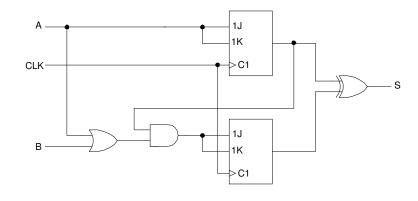

1. [2 val] Considere o circuito somador da figura abaixo.

De acordo com os valores lógicos indicados em cada uma das suas entradas, está-se a realizar a subtracção entre 2 números A e B representados em complemento para 2 e pertencentes ao intervalo [-8,+7].

Indique quais os valores decimais de A e B e quais os valores lógicos nas saídas do circuito. Justifique.

$$\begin{array}{c}

1 \\

1110 \\

1111 = -1 \\

+0101 \\

10100 \\

+4

\end{array}$$

Em Q está o complemento para 1 de B, portanto Q+CI faz o complemento para 2 de B.

Em P está A.

$$A = +5 = 0101$$

$B = +1 = 0001$  (complemento para 2 de -1 = 1111)

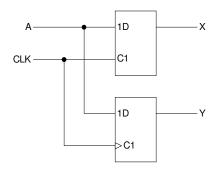

**2.** [2 val] Considere o circuito da figura e as formas de onda indicadas. Considere ainda X e Y inicialmente a 0. Esboce as formas de onda dos sinais X e Y, considerando os tempos de atraso dos elementos de memória desprezáveis face ao período de relógio.

O Latch lê a entrada A enquanto CLK=1.

O FF lê a entrada A apenas durante o flanco positivo do CLK.

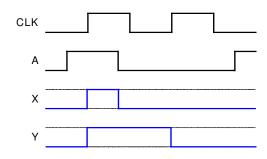

**3.** a) [3 val] Considere o circuito da figura. Considere inicialmente Q1=Q0=0 (e J=1,D=0). Esboce as formas de onda dos sinais D, J, Q1 e Q0 tendo em conta as formas de onda indicadas no diagrama temporal para o relógio de frequência 12,5 MHz e para a entrada E, as características temporais dos elementos de circuito indicadas na tabela, e a escala indicada.

b) [1 val] Existe algum problema de violação de SETUP? Justifique.

a)

A variação de E faz D mudar de 0 para 1, 10ns (tPLH do OR) após a variação de E.

Na transição positiva de relógio D=1 e J=K=1, logo Q0 vai mudar para 1 20ns (tPLH do FFD) após a variação do CLK, e Q1 vai mudar para 1 30ns (tPLH do FFJK) após a variação do CLK.

As variações de Q0 e Q1 de 0 para 1, vão provocar a variação de J de 1 para 0, 20ns (tPHL do NAND) após a variação do Q1 (último a chegar a 1).

b)

Não existem violações de SETUP:

A entrada D não varia nos  $10\,\mathrm{ns}$  (tSETUP do FFD) anteriores ao flanco positivo de relógio, e as entradas J e K não variam nos  $15\,\mathrm{ns}$  (tSETUP do FFJK) anteriores ao flanco positivo de relógio

**4.** [2 val] Indique qual é o período mínimo do relógio CLK que garante o funcionamento correcto do circuito, tendo em consideração as características temporais das portas lógicas e dos elementos de memória indicadas na tabela abaixo.

| FF JK              |       |  |  |  |  |  |

|--------------------|-------|--|--|--|--|--|

| $t_{SETUP}$        | 5 ns  |  |  |  |  |  |

| $t_{HOLD}$         | 2 ns  |  |  |  |  |  |

| $t_{PHL}$          | 10 ns |  |  |  |  |  |

| $t_{PLH}$          | 10 ns |  |  |  |  |  |

| AND                |       |  |  |  |  |  |

| $t_{\mathrm{PHL}}$ | 20 ns |  |  |  |  |  |

| $t_{PLH}$          | 20 ns |  |  |  |  |  |

| OR                 |       |  |  |  |  |  |

| $t_{\mathrm{PHL}}$ | 14 ns |  |  |  |  |  |

| $t_{PLH}$          | 14 ns |  |  |  |  |  |

| XOR                |       |  |  |  |  |  |

| $t_{\mathrm{PHL}}$ | 26 ns |  |  |  |  |  |

| $t_{PLH}$          | 26 ns |  |  |  |  |  |

Só existe um caminho de propagação de sinal entre FFs, e este caminho inclui apenas o FFJK e a porta AND.

$$\begin{split} t_{P\text{max}} &= \max \begin{cases} t_{PHL\_JK} + t_{PHL\_AND} = 10 + 20 = 30 ns \\ t_{PLH\_JK} + t_{PLH\_AND} = 10 + 20 = 30 ns \end{cases} \\ T_{CLK \, \text{min}} &= t_{P \, \text{max}} + t_{SETUP\ \ JK} = 35 ns \end{split}$$

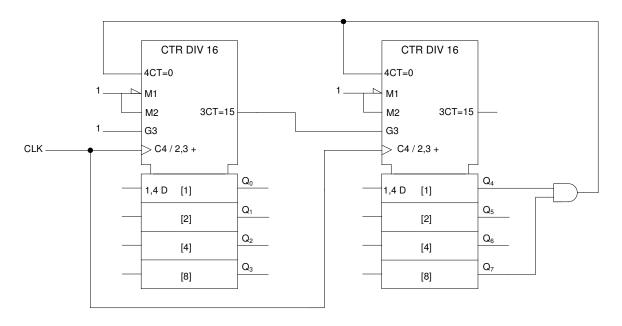

**5.** [2 val] Concretize um contador binário módulo 145, que conte de 0 a 144, utilizando os contadores abaixo e uma úmica porta lógica adicional. Justifique.

144=1001 0000

Ambos os contadores estão sempre em modo de contagem, M2=1. O contador da direita (4 bits de maior peso) é habilitado (entrada G3) pelo fim de contagem (saída 3CT=15) do contador da esquerda (4 bits de menor peso).

Quando é detectado o estado 144 é activada a entrada de inicialização (4CT=0) para que ambos os contadores transitem para o estado 0. O estado 144 é o primeiro em que Q7=Q4=1, portanto basta fazer o AND de Q7 com Q4 para detectá-lo.

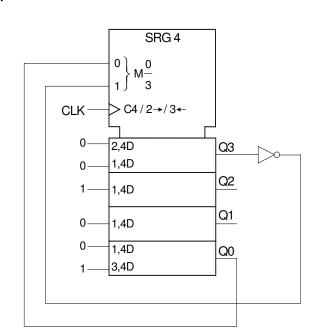

**6. a)** [3 val] Com o registo de deslocamento abaixo e uma única porta lógica adicional, projecte um circuito que concretize a sequência indicada ao lado.

b) [1 val] Indique o que acontece se o registo se iniciar no estado 0.

a) Conforme indicado no símbolo:

o modo 2 faz um deslocamento à direita (de cima para baixo, no componente),

o modo 3 faz um deslocamento à esquerda (de baixo para cima, no componente),

o modo 1 faz um carregamento paralelo.

| Q3 | Q2 | Q1 | Q0 | Operação a<br>realizar | M1 | M0 | SIN2 | SIN3 | D3 | D2 | D1 | D0 |

|----|----|----|----|------------------------|----|----|------|------|----|----|----|----|

| 0  | 1  | 0  | 0  | SHIFT RIGHT            | 1  | 0  | 0    | X    | X  | X  | X  | X  |

| 0  | 0  | 1  | 0  | SHIFT RIGHT            | 1  | 0  | 0    | X    | X  | X  | X  | X  |

| 0  | 0  | 0  | 1  | SHIFT LEFT             | 1  | 1  | X    | 1    | X  | X  | X  | X  |

| 0  | 0  | 1  | 1  | SHIFT LEFT             | 1  | 1  | X    | 1    | X  | X  | X  | X  |

| 0  | 1  | 1  | 1  | SHIFT LEFT             | 1  | 1  | X    | 1    | X  | X  | X  | X  |

| 1  | 1  | 1  | 1  | LOAD                   | 0  | 1  | X    | X    | 0  | 1  | 0  | 0  |

Directamente da tabela:

$$M1 = \overline{O3}$$

$$M0 = Q0$$

$$SIN2 = 0$$

$$SIN3 = 1$$

$$D3 = 0$$

$$D2 = 1$$

$$D1 = 0$$

$$D0 = 0$$

b)

No estado 0 (Q3=Q2=Q1=Q0=0), M1=1 e M0=0 e portanto o registo vai fazer um deslocamento à direita. Como a entrada série respectiva está a 0, o registo mantém-se no estado 0.

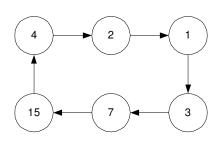

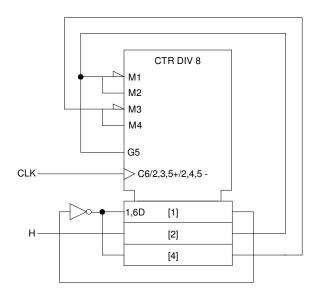

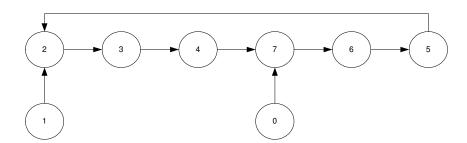

7. a) [2,5 val] Indique a sequência de estados, começando no estado 2 e até voltar ao estado 2, concretizada pelo circuito abaixo.

b) [1,5 val] Este circuito tem problemas de lockout? Justifique.

a) Conforme indicado no símbolo:

Contagem ascendente: precisa das entradas 2, 3 e 5 activas (além do relógio). Contagem descendente: precisa das entradas 2, 4 e 5 activas (além do relógio). Carregamento paralelo: precisa da entrada 1 activa (além do relógio). A entrada G5 está sempre activa quando M2 está activo.

$$M 2 = Q1$$

$$M 4 = Q2$$

$$D2 = D0 = \overline{Q0}$$

$$D1 = 1$$

| Esta | tual | Modo |    | Operação | Estado Seguinte |    |    |    |

|------|------|------|----|----------|-----------------|----|----|----|

| Q2   | Q1   | Q0   | M2 | M4       | Operação        | Q2 | Q1 | Q0 |

| 0    | 1    | 0    | 1  | 0        | +               | 0  | 1  | 1  |

| 0    | 1    | 1    | 1  | 0        | +               | 1  | 0  | 0  |

| 1    | 0    | 0    | 0  | 1        | LOAD            | 1  | 1  | 1  |

| 1    | 1    | 1    | 1  | 1        | _               | 1  | 1  | 0  |

| 1    | 1    | 0    | 1  | 1        | _               | 1  | 0  | 1  |

| 1    | 0    | 1    | 0  | 1        | LOAD            | 0  | 1  | 0  |

b)

Estado  $0 = 000 \rightarrow \text{LOAD } 111 \rightarrow \text{Estado } 7 \rightarrow \text{Não provoca } lockout.$ Estado  $1 = 001 \rightarrow \text{LOAD } 010 \rightarrow \text{Estado } 2 \rightarrow \text{Não provoca } lockout.$

Este circuito não tem, portanto, problemas de lockout.